(An ISO 3297: 2007 Certified Organization) Vol. 5, Special Issue 5, March 2016

# FPGA Based Power Factor Improvement Using Single Phase Matrix Converter

R.Annadurai<sup>1</sup>, K.Sowmiya<sup>2</sup>

Assistant Professor, Dept. of EEE, Arunai Engineering College, Thiruvannamalai, Tamilnadu, India<sup>1</sup>

PG Student [PED], Dept. of EEE, Arunai Engineering College, Thiruvannamalai, Tamilnadu, India<sup>2</sup>

**ABSTRACT**: This project presents a new approach for converting three phase AC power to single phase using a simple circuit topology with bidirectional switches that are triggered by logically generated gating pulses. Power Factor of the system get improved by controlling the SPWM and IGBT switching control through FPGA control with help of XILINX system. The phase converter chosen in this work involves single stage power conversion principle and is capable of providing a variable voltage, variable frequency but constant v/f single phase output voltage from available three phase source using Matrix Converter (MC). The performance of the chosen phase converter is evaluated in MATLAB/SIMULINK environment for different types of load. This implementation of SPMC based phase converter is also carried out using low cost but powerful FPGA and the experimental results obtained are compared with those obtained through simulation. The significant application of this phase conversion technique is simplified feeder mechanism for electric locomotives.

KEYWORDS: FPGA, Transformer, Rectifier, Regulator, Detector(XILINX Software).

### **I.INTRODUCTION**

Three phase variable speed drives for asynchronous motors have been used more and more, especially in energy saving drive applications. In many cases, the cost reduction is an important target for the drive. Hence, a reduced number of inverter switches is a promising solution. The speed of the induction motor can be controlled by varying its input AC voltage and frequency. Several inverter schemes with reduced number of switches have been proposed. Among them the four switch three phase inverter (B4) was introduced with four IGBT switches instead of six (B6) in a conventional three phase inverters. The 4S3P inverter, which uses only four switches to produce three phase output voltages, is the suggested topology with a low cost. The modulation strategies have been developed based on space vectors. Compared with the SPWM method, the space vector PWM (SVPWM) method has been shown to generate less total harmonic distortion in output voltages and currents, less switching loss and a wide linear modulation region.

#### **II. PROPOSED SYSTEM**

A single phase using a simple circuit topology with bidirectional switches that are triggered by logically generated gating pulses. The performance of the chosen phase converter is evaluated in MATLAB/SIMULINK split phase induction motor of load. This implementation of SPMC based phase converter is also carried out using low cost but powerful FPGA and the experimental results obtained are compared with those obtained through simulation. The results obtained validate the strategy developed. Power factor of this single phase matrix converter improved by controlling the ON and OFF time period of IGBT switches and controlling PWM switching period with help of FPGA and Xilinx 13.2 Software.In many instances, the single phase load is supplied by one phase of three phase service when single phase service is not available. Supplying high power density single phase load like electric traction becomes prohibitive due to occurrence of higher negative sequence currents in the power grid which causes over heating of aldevices 2 connected to the grid.

#### **III.PROPOSED SYSTEM**

The phase converter chosen in this work involves single stage power conversion principle and is capable of providing a variable voltage, variable frequency but constant v/f single phase output voltage from available three phase source using Matrix Converter (MC). The proposed circuit topology is capable of operating a single phase AC motor under

(An ISO 3297: 2007 Certified Organization)

### Vol. 5, Special Issue 5, March 2016

constant v/f mode eliminating the occurrence of negative sequence currents in the power system network as it tends to create balanced loading of all three phases.

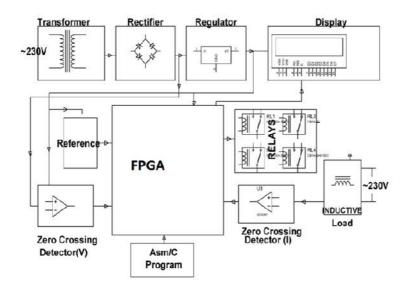

Fig 1 Proposed block diagram

The mathematical model of the proposed converter , which is supplied by a three-phase ac source and the phase voltages are denoted as van, vbn, and vcn, respectively. A three-phase to single-phase matrix converter, which composes of three boost inductors (La, Lb, and Lc) and six bidirectional switches (Sa1, Sb1, Sc1, Sa2, Sb2, and Sc2), inserts between the ac source and a conventional N/2-stage CWVM circuit, where N is an even integer. Two anti-series Insulated Gate Bipolar Transistors (IGBTs) form one bidirectional switch as shown in the left-bottom part in Fig. 2. The six bidirectional switches are divided into two parts, the upper part (Sa1, Sb1 and Sc1) and the bottom part (Sa2, Sb2, and Sc2). According to the first subscripts of the switches, the left terminals of the switches connect to the relative ac sources through three boost inductors. The three right terminals of the upper-part switches connect to upper terminal D of the CWVM, while the three right terminals of the bottom-part switches connect to the part and the CWVM. For simplicity, the derivation of the mathematical model is divided into two parts, the ac-side part and the CWVM, which are separated by the terminals D and E.

#### **IV.SOFTWARE ANALYSIS**

Simulation has become a very powerful tool for industrial application as well as in academics, nowadays. It is now essential for an electrical engineer to understand the concept of simulation to study the system or circuit behaviour without damaging it .The tools for doing the simulation in various fields are available in the market for engineering professionals. Many industries are spending a considerable amount of time and money in doing simulation before manufacturing their product. In most of the research and development (R&D) work, the simulation plays a very important role. Without simulation it is quiet impossible to proceed further. It should be noted that in power electronics, computer simulation and a proof of concept hardware prototype in the laboratory are complimentary to each other. However computer simulation must not be considered as a substitute for hardware prototype. The objective of this chapter is to describe simulation of impedance source inverter with R, R-L and RLE loads using MATLAB tool.

Electrical power systems are combinations of electrical circuits and electro mechanical devices like motors and generators. Engineers working in this discipline are constantly improving the performance of the systems. Requirements for drastically increased efficiency have forced power system designers to use power electronic devices

(An ISO 3297: 2007 Certified Organization)

### Vol. 5, Special Issue 5, March 2016

and sophisticated control system concepts that tax traditional analysis tools and techniques. Further complicating the analyst's role is the fact that the system is often so nonlinear that the only way to understand it is through simulation. Land-based power generation from hydroelectric, steam, or other devices is not the only use of power systems. A common attribute of these systems is their use of power electronics and control systems to achieve their performance objectives.

| 🗃 olock                                                                     |                                                                     |                                                                    |                                                                   |        |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|--------|

| File Edit View Pavorites Tools                                              | Help                                                                |                                                                    |                                                                   | 12     |

| 🔇 Back = 🔘 - 🎓 🔎                                                            | Search 🍋 Folders 📊 -                                                |                                                                    |                                                                   |        |

| Address 🛅 U:\Research\Programs\clo                                          | ck                                                                  |                                                                    |                                                                   | 🛩 🛃 Go |

| File and Folder Tasks 🙁                                                     | Pile Polder                                                         | _xmsgs<br>Fife Folder                                              | rile Polder                                                       | ^      |

| Make a new folder Publish this folder to the Web Web Yiew previous versions | xat<br>File Folder                                                  | adder_subtracter_spartan3_7.<br>Adobe DRM Activation File<br>29 KB | binary_counter_spartan3_7_0<br>Adobe DRM Activation File<br>17 KB |        |

| Other Places *                                                              | sine_cosine_look_up_table_sp<br>Adobe DRM Activation File<br>100 KB | dock_cw.bgn<br>DGN File<br>6 KB                                    | clock_cwibit<br>BIT File<br>128 KB                                |        |

| Programs     My Documents     Shared Documents                              | clock_cw.bld<br>BLD File<br>2 KD                                    | dock_cw.cel<br>CEL File<br>0 KB                                    | clock_cw.cmd_log<br>CMD_LOG File<br>19 KB                         |        |

| G My Computer                                                               | vcom:do<br>DO File<br>1 KB                                          | dock_cw.drc<br>DRC File<br>1 KB                                    | clock_dw_vhd<br>File<br>11 KB                                     |        |

| Details (*)                                                                 | globals<br>File<br>1 KB                                             | hdiFiles<br>Filo<br>1.KB                                           | name_translations<br>File<br>3 KB                                 |        |

|                                                                             | synopsis<br>File<br>42 KB                                           | ultradistance_dw_vhd<br>File<br>11 KB                              | GIMP Image                                                        |        |

|                                                                             | GIMP image<br>I KB                                                  | Clock_cw_summary<br>HTTML File<br>7 KB                             | ISE File<br>347 KB                                                |        |

|                                                                             | clock_cw.ise_ISE_Backup<br>ISE_ISE_BACKUP File<br>347 KB            | LEP File<br>1 KB                                                   | LSO File<br>1 KB                                                  |        |

|                                                                             | Clock_cw_pad<br>Microsoft Office Excel Comma<br>12 KB               | sine_cosine_look_up_table_sp.<br>MIF File<br>3 KB                  | clock_cw_map.mrp<br>MRP File<br>11 KB                             |        |

|                                                                             | clock_cw.ncf                                                        | ultradistance_cw.ncf                                               |                                                                   | ~      |

Fig 2: XILINX ISE 13.2 document.

Once the file is open, only thing that needs to be done is to assign the pins to the output ports on the FPGA board. So click to expand (+) the user constraints in the processes window and double click on create area constraints. This will start to assemble the program, but will ask to add a UCF file halfway though implementing the design. After clicking yes, the PACE window will open as follows.

| Xillinx PACE - Us'Research/Programm'SimpleInventer/ultroplateventer_ow.ucf     He Edt Vice DOS areas Tools Window Hep |            |                                                                             |                    |  |  |

|-----------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------|--------------------|--|--|

| D 🖉 🗟 🕫 🕷 🇯                                                                                                           | 略 医哈马曼 医核系 | 8 8 4 5 7 7 7 7 7 1 2 3 3 4 3 4 4 9 1 5 5 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 |                    |  |  |

| Deelge Browner<br>* 210 Pris<br>* 6kbellogie<br>T Logie                                                               |            | Device Architecture for xc35 200 4 11256                                    | <u>lehter</u><br>2 |  |  |

| C C C C C C C C C C C C C C C C C C C                                                                                 |            |                                                                             |                    |  |  |

| <u>  ( )</u>                                                                                                          |            | NExter 200 Annue area /                                                     |                    |  |  |

#### Fig 3: Design of FPGA.

In this window, all the pins from the Simulink gateways show up as I/O pins. To route them out of the board, all that need to be done is type in the I/O pin number (the pins numbers can be found written on the board for switches and LED"s and in the users guide pg 49-51 for the I/O connectors). Set the input pin to K13 and the output to K12. From this point, the project is complete and ready to be assembled and implemented as a normal Xilinx program. 34

To do this expand "Generate Programming File" under the Processes tab and double click on "Configure Device (impact)." Click FINISH on the pop-up "Welcome to IMPACT." Two Xilinx icons appear on the screen along with the

(An ISO 3297: 2007 Certified Organization)

### Vol. 5, Special Issue 5, March 2016

"Assign New Configuration File" pop-up..For the next pop-up just cancel. Now highlight the first Xilinx icon and right click and Program. This should download your program to the Xilinx board. Demonstration the operation of your program with SW7 and LD0.

| Co e te        |                                              |       |                 |                                                           |      |                                                                   |        |                                                                   |        |

|----------------|----------------------------------------------|-------|-----------------|-----------------------------------------------------------|------|-------------------------------------------------------------------|--------|-------------------------------------------------------------------|--------|

| //Piller       | Edit View Pavorites                          | Tools |                 |                                                           |      |                                                                   |        |                                                                   | Ar     |

| -              | Back • 🕥 · 📂                                 | Se Se | arch            | Folders                                                   |      |                                                                   |        |                                                                   | 🛩 🛃 Go |

|                |                                              |       |                 |                                                           |      |                                                                   |        |                                                                   |        |

| and set of the | le and Folder Tasks                          | (\$   |                 | File Folder                                               |      | File Folder                                                       |        | File Folder                                                       |        |

|                | Make a new folder Publish this folder to the |       | -               |                                                           | 1 00 | adder subtracter spartap3 7                                       | -      | bioary counter spartap3 7 0                                       |        |

|                | Web<br>View previous versions                |       |                 | xst<br>Pile Polder                                        | 51   | adder_subtracter_spartan3_7<br>Adobe DRM Activation File<br>29 KB | 20     | binary_counter_spartan3_7_0<br>Adobe DRM Activation File<br>17 KB |        |

|                |                                              |       | De De           | sine_cosine_look_up_table_sp<br>Adobe DRM Activation File |      | clock_cw.bgn                                                      |        | clock_cw.bit                                                      |        |

| - 01           | ther Places                                  | *     | 1               | Adobe DRM Activation File<br>100 KB                       | 322  | ISGN Pile<br>IS KB                                                | 222    | BIT File<br>125 KB                                                |        |

| 6              | Programs<br>My Documents                     |       | [mmm]           | clock_cw.bld                                              | -    | clock_cw.cel                                                      |        | clock_cw.cmd_log<br>CMD_LOG_Pile                                  |        |

| 6              | Shared Documents                             |       | 323             | 2.KB                                                      | 222  | O KB                                                              | 202    | 19 KB                                                             |        |

| 5              | My Computer                                  |       |                 | vcom.do<br>DO File                                        |      | clock_cw.drc<br>DRC File                                          |        | clock_dw_vhd                                                      |        |

|                | My Network Places                            |       | LESSI           | 1 KB                                                      | 1938 | 1 KB                                                              | 12.2.2 | 11 KB                                                             |        |

| D              | ntails                                       |       | [222]           | globals<br>File                                           |      | hdl#les<br>rife                                                   | [222]  | name_translations                                                 |        |

|                |                                              |       | Land            | 1 803                                                     |      | 1 KB                                                              | (aaa)  | 3 KB                                                              |        |

|                |                                              |       | [333]           | eynopele<br>File                                          | 333  | ultradistance_dw_vhd<br>Pile                                      |        | GIMP image                                                        |        |

|                |                                              |       | Land            | 42 KB                                                     |      | 11 KB                                                             | -      |                                                                   |        |

|                |                                              |       | -               | GIMP image<br>1 KB                                        | C    | clock_cw_summary<br>HTML File<br>7 KB                             | ISE    | Clock_cve<br>ISE File<br>347 KB                                   |        |

|                |                                              |       |                 |                                                           |      | clock cw.lfp                                                      |        | clinik cur ho                                                     |        |

|                |                                              |       | 222             | clock_cwitee_ISE_Backup<br>ISE_ISE_BACKUP File<br>347 FB  | 335  | LPP rile                                                          | 1000   | LSO Pile<br>1 KD                                                  |        |

|                |                                              |       | and the second  | clock cw pad                                              |      | sine_cosine_look_up_table_sp                                      |        | clock cw map.mrp                                                  |        |

|                |                                              |       | <sup>™</sup> a, | Microsoft Office Excel Comma<br>12 kB                     | 111  | MIF File<br>3 KB                                                  | 202    | MRP File<br>11 KB                                                 |        |

|                |                                              |       |                 | clock_cw.ncf                                              |      | ultradistance_cw.ncf                                              | -      | clock_cw                                                          | ~      |

Fig 4: XILINX ISE 13.2 document

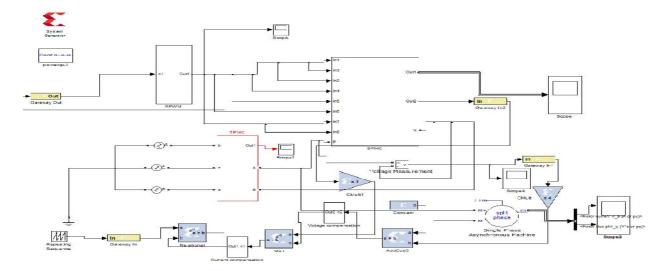

The performance of the proposed control methods was evaluated first using a detailed simulation model representing the Three-phase to single MC, and additional blocks to simulate the control system using MATLAB/ Simulink SimPowerSystems tool-ox. MC semiconductors were simulated as SimPowerSystem switches with appropriate snubbers. The Single phase Matrix PFC converter is designed with the following specifications: ac input voltage range from 400V to 440V, output voltage equal to 200 to 230V, output power up to 650W, line frequency (f) equal to 60 Hz, switching frequency (fs) equal to 130kHz.

The CCM current compensator is designed in MATLAB SISO tool to achieve the desired response characteristics, and the designed continuous-time transfer function of the average current compensator is given by The current compensator is implemented using the Xilinx block set, the compensator is designed based on the direct form-2 structure of transfer function (4) as shown in below

### VI. SIMULATION RESULTS

Fig 4 Simulation diagram

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Special Issue 5, March 2016

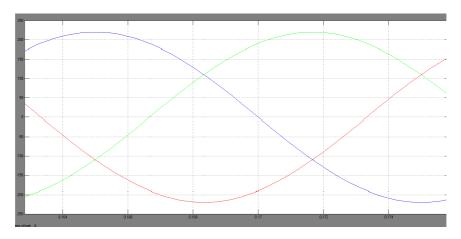

### A.THREE PHASE INPUT CURRENT

### **B. THREE PHASE INPUT CURRENT**

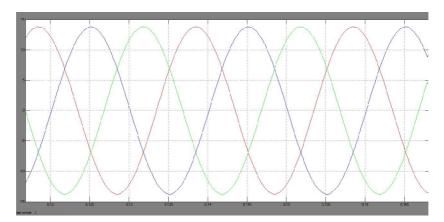

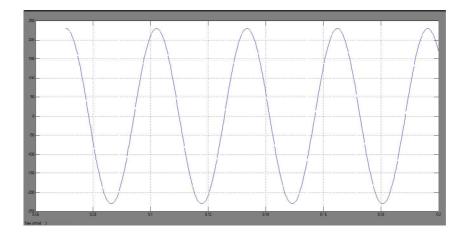

### C. OUTPUT WAVEFORM

(An ISO 3297: 2007 Certified Organization)

### Vol. 5, Special Issue 5, March 2016

#### **VII.CONCLUSION**

A FPGA system used to improve power factor and also give the sinusoidal output waveform by controlling the SPWM and IGBT switching control with help of XILINX SYSTEM. This work also facilitates to monitor the power factor changes in system. The system control strategy is fully developed and all the simulation results are presented. Because of the decrease in the switching time, the rating of switches decreases in converter circuit of proposed configuration which may helps in reducing cost of the system. Simulations of digital controller for TPSPMC PFC converter have been done on the platform of MATLAB Simulink environment and Xilinx System generator. Both voltage and current compensators have been generated from Xilinx System generator to control PFC converter. The FPGA based digital controller can be synthesis using Xilinx ISE design tools resulted in the above simulation results for as target FPGA.

#### REFERENCES

[1] Yang-Lin Chen, Hong-JyunChen, Yaow-Ming, and Chen, KwanH.Liu, "A stepping on-time adjustment method for interleaved multichannel PFC converters," *IEEE Transactions On Power Electronics*, vol.30, no.3, March 2015.

[2] Qing Ji,XinboRuan, and Zhihong Ye, "The worst conducted EMI spectrum of critical conduction mode boost type converter," *IEEE Transactions On Power Electronics*, vol.30, no.3, March 2015.

[3] MarcioSilveriaOrtmann, Thiago Batista Soeiro ,andMaercelo Lobo Heldwein , "High switches utilization single phase PWM boost type PFC rectifier topologies multiplying the switching frequency," *IEEE Transactions On Power Electronics*, vol.29, no.11, November 2014.

[4] SeungbumLim, David M. Otten, and David J. Perreault, "New AC-DC power factor correction architecture suitable for high frequency operation" *IEEE Transactions On Power Electronics*, DOI 10.1109/TPEL 2015.2445927.

[5] XueshanLiu, JianpingXu, Zhangyong, and Nan Wang, "Single –inductor dual output buck boost power factor correction converter," *IEEE Transactions On Industrial Electronics*, DOI 10.1109/FIE .2014.2334659.

[6] Nikita kolte, and N.B. Wagh, "Comparative analysis of power factor correction techniques for AC/DC converter at various load," *ISSN International Advanced Research Journal In Science, Engineering and technology*, vol.1, Issue.2, October 2014.